电源、时钟、复位管理

电源管理

电源引脚

SOC 外部为什么有多组 VDD/VSS

原因主要有以下几点:

芯片内部有很多功能单元,这些单元都需要供电,采用多引脚供电可以就近获取电源,无需在内部穿越。

存在多个电源域,不同单元之间,有时不希望电源互相影响,采用独立的电源引脚,可以避免这种影响。所以,多组VDD之间可能不连通

实际使用时,每个引脚不但要连接电源,还应在电源引脚附近加上退藕电容。其目的是当器件工作时,电流的变化会引起电源的电压微小波动,加上退藕电容后,这种波动就不容易传递到另外的电源引脚。

在电路设计中对供电引脚需要考虑几点:

- 尽管所有VDD和所有VSS在内部相连,在芯片外部仍然需要连接上所有的VDD和VSS。因为导线较细,内部连接负载能力较差,抗干扰的能力也较差,如果漏接VDD或VSS,容易造成内部线路损坏,同时抗干扰能力下降

- 每对VDD与VSS都必须在尽可能靠近芯片处放置滤波电容

VDD / VDDA /VDDIO

VDD 表示主电源、VDDA 为模拟部分供电电源,而 VDDIO 则是 GPIO 供电电源。一些芯片将这三类电源分别用单独电源引脚引出,但其一般共用一个电源,电源之间压差有具体要求,具体参考 datasheet,也有芯片直接整合为一种类型的 VDD 引脚。

内部 LDO

一些专用芯片如车用芯片,内置高压 LDO,可用于只有单一高压电源的系统,因此不需要为其生成额外的电源,以减少外部电源器件使用以及提高稳定性,内部 LDO 可能需要外接 R/C 等辅助器件。当然除了使用内置高压 LDO,也可允许用户使用正常的 VDD.

一些低功耗芯片也有内置低电压的 LDO,以满足特殊需求。

电源域

为满足 SOC 不同工作模式的功耗等要求,通常将内部电源控制划分不同的区域,以根据实际需求细分电源供应区域。不同电源域之间电压不一定相同,同时支持根据实际功耗要求允许通过配置寄存器方式开闭相应外设的电源。

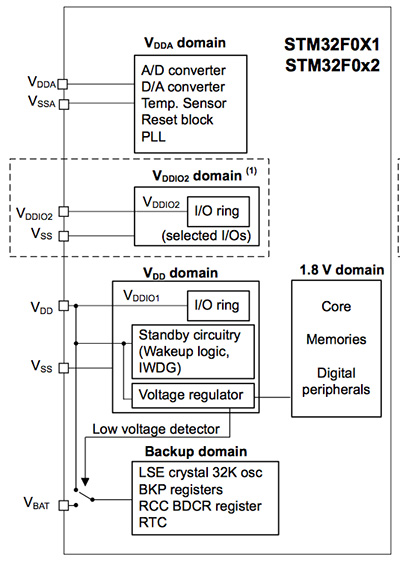

下图展示stm32f0x电源电源域

电源监视器

电源监视器当检测到器件供电电压发生变化时产生复位等动作,常见的有:

上电复位 (POR) 和 掉电复位 (PDR)

当 VDD/VDDA 低于指定阈值 VPOR/PDR 时,器件无需外部复位电路便会保持复位状态。有关上电/掉电复位阈值的相关详细信息,请参见数据手册的电气特性部分

欠压复位 (PDR)

上电期间,欠压复位 (BOR) 将使器件保持复位状态,直到电源电压达到指定的 VBOR 阈值,VBOR 阈值高于 VPOR/PDR,其阈值允许用户配置

可编程电压检测器 (PVD)

指示 VDD 是大于还是小于 PVD 阈值,并产生相应的中断事件,该功能的用处之一就是可以在中断服务程序中执行紧急关闭系统的任务。

时钟配置

时钟源

一般 MCU 时钟源分为内部以及外部两大类型,同时根据时钟快慢又细分为高速时钟以及低速时钟两类,即 HSE、LSE、HSI、LSI. 还有一些用于特定外设的固定时钟源。外部高速时钟一般为 MHz 单位为主要的时钟源,而外部低速时钟一般为 32.768 kHz,用于 RTC、WDT 等提供时钟源。外部时钟一般为无源晶振或者时钟信号输入,而内部时钟源一般为 RC 振荡器,其震荡频率精度不高且频率较低。具体器件应查看 datasheet 确定其时钟源有哪些

时钟树

时钟源出来的时钟并不直接时钟,一般需要经过分频以及倍频的处理以分别提供给内核、总线、外设等组件。时钟配置一般以树状结构方式以可视化配置,一般 MCU 内部存在多个 PLL 以及 分频器以配置合适的时钟,一般时钟类型分为:

- 系统核心时钟

- 总线时钟

- 外设时钟(按需使能以降低功耗)